1. HIMPP平台架构简介

海思提供的媒体处理软件平台(Media Process Platform,简称 MPP),可支持应用软件快速开发。该平台对应用软件屏蔽了芯片相关的复杂的底层处理,并对应用软件直接提供 MPI(MPP Program Interface)接口完成相应功能。该平台支持应用软件快速开发以下功能:输入视频捕获、H.265/H.264/JPEG 编码、H.265/H.264/JPEG 解码、视频输出显示、视频图像前处理(包括去噪、增强、锐化)、图像拼接、图像几何矫正、智能、音频捕获及输出、音频编解码等功能。

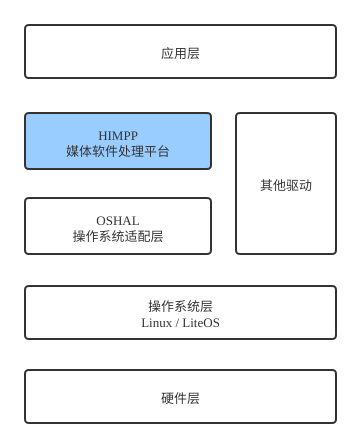

2. 系统分层结构

系统大概层次结构如下:

- 硬件层

硬件层由 Hi35xx 芯片加上必要的外围器件构成。外围器件包括 Flash、DDR、视频 Sensor 或 AD、音频 AD 等。 - 操作系统层

基于 Linux 或 Huawei LiteOS 的 OS 系统。 - 操作系统适配层

提供操作系统系统调用基础函数,屏蔽操作系统差异,支持媒体处理平台运行在不同的操作系统上,或相同操作系统不同版本。 - 媒体处理平台

基于操作系统适配层,控制芯片完成相应的媒体处理功能。它对应用层屏蔽了硬件处理细节,并为应用层提供 API 接口完成相应功能。 - 其他驱动

除媒体处理平台外,海思为 Hi35xx 芯片的其他相关硬件处理单元提供了相应的驱动,包括 CIPHER、RTC 等驱动。 - 应用层

基于海思媒体处理平台及其他驱动,由用户开发的应用软件系统。

以上这些分层,我们主要关注的是 HIMPP 媒体软件处理平台和应用层。我们必须对 HIMPP 这层的内容进行深入的学习了解,才能在其基础之上开发应用。

3. HIMPP 数据处理流程

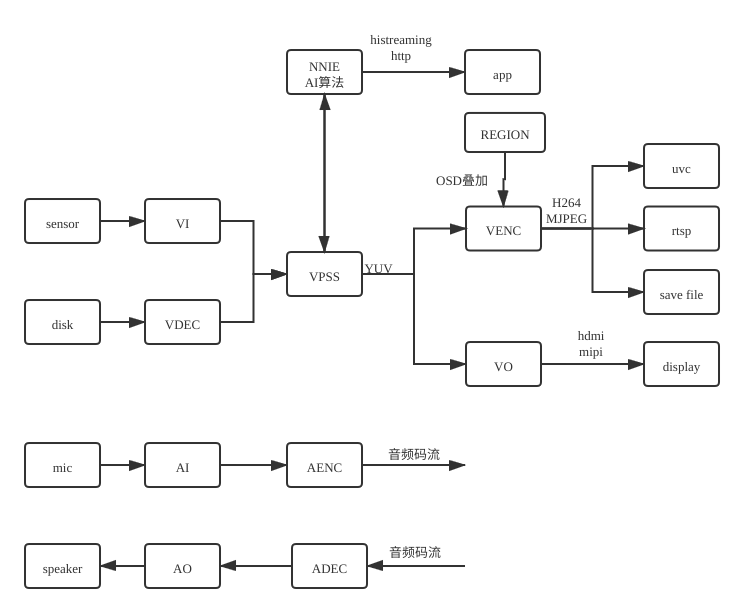

海思媒体处理平台主要流程分为视频处理及音频处理两条路线:

我们先来大概了解一下各个模块的作用:

- sensor: 包括镜头,感光芯片等器件,主要作用是光电信号转换。

- disk: 为硬盘存储文件。视频的来源既可以是从 sensor 中采集的,也可以是从文件中读取出来的。视频回放时走的是这条通路。

- VI:视频采集模块。捕获视频图像,可对其做剪切、缩放、镜像等处理,并输出多路不同分辨率的图像数据。

- VDEC:视频解码模块。对编码后的视频码流进行解码,并将解析后的图像数据送 VPSS 进行图像处理或直接送 VO 显示。可对 H.264/H.265/VC1/MPEG4/MPEG2/AVS 格式的视 频码流进行解码。

- VPSS:图像处理子系统。接收 VI 或 VDEC 发送过来的图像,可对图像进行去噪、图像增强、锐化等处理,并实现同源输出多路不同分辨率的图像数据用于编码、预览或抓拍。

- NNIE:AI算法模块。从 VPSS 拿到帧数据,然后进行人脸检测,识别等各种 AI 算法。算法结果可以通过 histreaming 等协议发送给客户端 app。

- VENC:编码模块。接收 VI 捕获并经 VPSS 处理后输出的图像数据,可叠加用户通过 Region 模块设置的 OSD 图像,然后按不同协议进行编码并输出相应码流(H264,MJPEG等)。然后可以通过各种视频传输协议进行传输。比如 uvc, rtsp, http 等。也可以保存到文件,后续可以进行回放。

- VO:视频输出模块。接收 VPSS 处理后的输出图像,可进行播放控制等处理,最后按用户配置的输出协议输出给外围视频设备 HDMI 等。

- mic:麦克风。主要作用是声电信号转换。

- AI: 音频采集模块。捕获音频数据,然后 AENC 模块支持按多种音频协议对其进行编码,最后输出音频码流。

- 用户从网络或外围存储设备获取的音频码流可直接送给 ADEC 模块,ADEC 支持 解码多种不同的音频格式码流,解码后数据送给 AO 模块即可播放声音。

我们对以上各模块的作用及数据处理流程一定要非常熟悉。因为应用层的开发基本上都是围绕着这个流程来进行编码实现的。应用层只需要配置好各模块的参数,启动,然后把各模块连接起来就行。

4. 系统初始化

系统控制模块根据芯片特性,完成硬件各个部件的复位、基本初始化工作,同时负责完成 MPP(Media Process Platform 媒体处理平台)系统各个业务模块的初始化、去初始化以及管理 MPP 系统各个业务模块的工作状态、提供当前 MPP 系统的版本信息、提供大块物理内存管理等功能。应用程序启动 MPP 业务前,必须完成 MPP 系统初始化工作。同理,应用程序退出 MPP 业务后,也要完成 MPP 系统去初始化工作,释放资源。

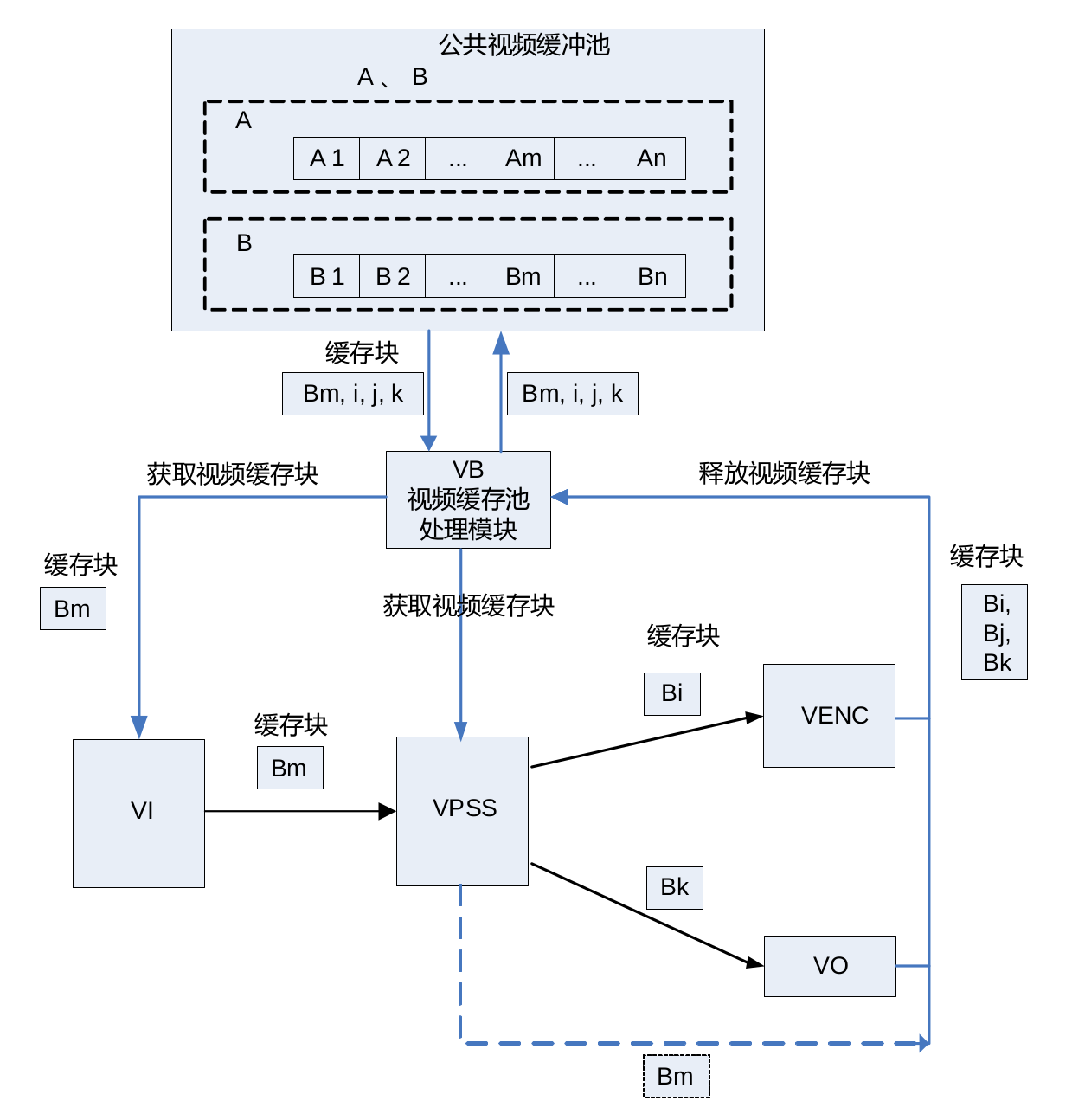

4.1 视频缓冲池 VB

视频缓存池主要向媒体业务提供大块物理内存管理功能,负责内存的分配和回收,充分发挥内存缓存池的作用,让物理内存资源在各个媒体处理模块中合理使用。一组大小相同、物理地址连续的缓存块组成一个视频缓存池。

视频输入通道需要使用公共视频缓存池。所有的视频输入通道都可以从公共视频缓存池中获取视频缓存块用于保存采集的图像(如图中所示从公共视频缓存池 B 中获取视频缓存块 Bm)。由于视频输入通道不提供创建和销毁公共视频缓存池功能,因此,在系统初始化之前,必须为视频输入通道配置公共视频缓存池。

典型的公共视频缓存池数据流图如下:

VI 从公共视频缓存池 B 中获取视频缓存块 Bm,缓存块 Bm 经 VI发送给 VPSS,输入缓存块 Bm 经过 VPSS 处理之后被释放回公共视频缓存池。假设 VPSS 通道的工作模式是 USER, 则 VPSS 通道 0 从公共视频缓存池 B 中获取缓存块 Bi 作为输出图像缓存 buffer 发送给 VENC,VPSS 通道 1 从公共视频缓存池 B 中获取缓存块 Bk 作为输出图像缓存 buffer 发送给 VO,Bi 经 VENC 编码完之后释放回公共视频缓存池,Bk 经 VO 显示完之后释放回公共视频缓存池。

5. VI

视频输入(VI)模块实现的功能:通过 MIPI Rx(含 MIPI 接口、LVDS 接口和 HISPI 接口),SLVS-EC,BT.1120,BT.656,BT.601,DC 等接口接收视频数据。VI 将接收到的数据存入到指定的内存区域,在此过程中,VI 可以对接收到的原始视频图像数据进行处理, 实现视频数据的采集。

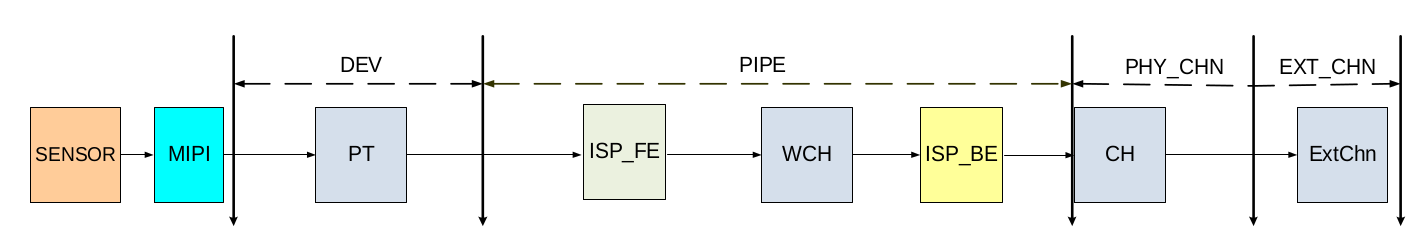

VI 在软件层次上划分 4 个部分:

VI 从软件上划分了输入设备(DEV), 输入 PIPE(图示为物理 PIPE,虚拟 PIPE 只包含ISP_BE)、物理通道(PHY_CHN)、扩展通道(EXT_CHN)四个层级。

- 视频输入设备

视频输入设备支持若干种时序输入,负责对时序进行解析。 - 视频输入物理 PIPE

视频输入 PIPE 绑定在设备后端,负责设备解析后的数据再处理。包含了 ISP 的相关处理功能,主要是对图像数据进行流水线处理,输出YUV 图像格式给通道。 - 视频输入虚拟 PIPE

视频输入虚拟 PIPE 不绑定设备,负责其他模块或用户发送过来的数据再处理。 - 视频物理通道

物理通道负责将最终处理后的数据输出到 DDR,在真正将数据输出到 DDR 之前,它可以实现裁剪等功能。Hi3519AV100 VI 的一个 PIPE 包含 2 个物理通道。CH0 具有裁剪、压缩等功能。CH1 具有缩小的功能,支持 8 个扩展通道。 - 视频扩展通道

扩展通道是物理通道的扩展,扩展通道具备缩放、裁剪、鱼眼矫正功能,它通过绑定物理通道,将物理通道输出作为自己的输入,然后输出用户设置的目标图像。

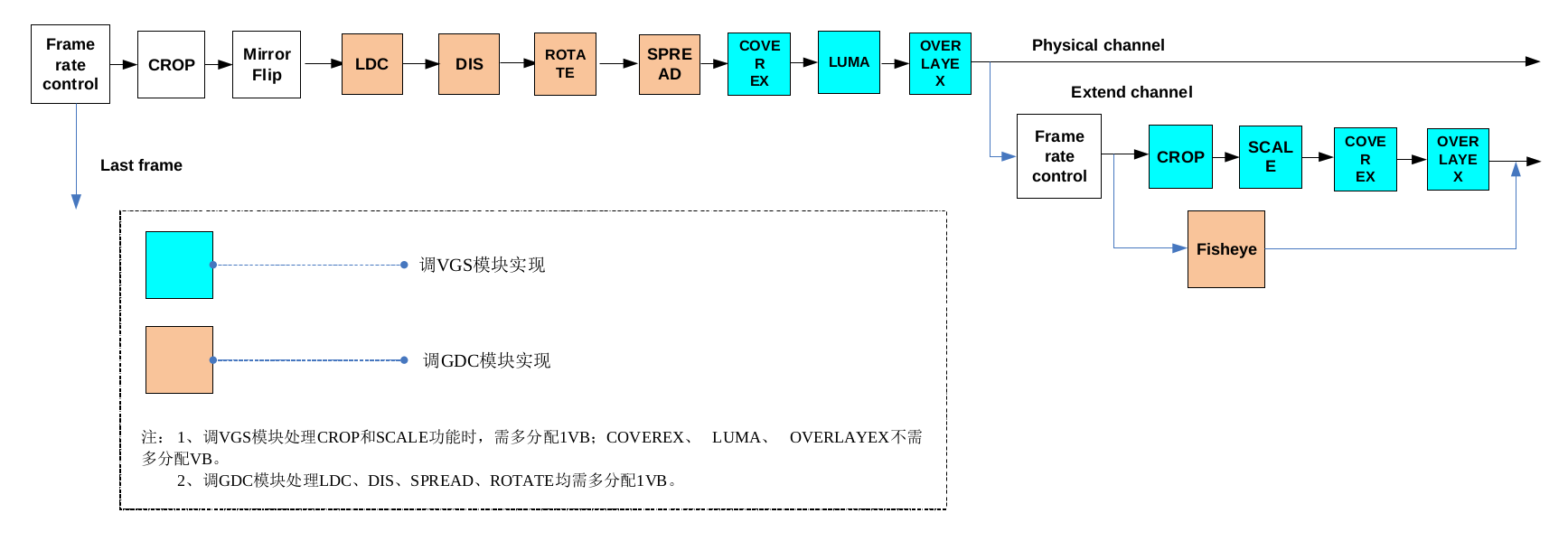

VI 的硬件通路如下:

- 镜头畸变校正(LDC)

镜头畸变校正,一些低端镜头容易产生图像畸变,需要根据畸变程度对其图像进行校正。 - DIS

DIS 模块通过比较当前图像与前两帧图像采用不同自由度的防抖算法计算出当前图像在各个轴方向上的抖动偏移向量,然后根据抖动偏移向量对当前图像进行校正,从而起到防抖的效果。 - BAS

Bayer scaling,即 Bayer 域缩放。 - 低延时

低延时指图像写出指定的行数到 DDR 后,VI 上报一个中断,把图像发给后端模块处理,可以减少延时,且硬件会有机制保证图像是先写后读,不会出现读图像错误。 - 提前上报中断

提前上报中断指图像写出指定的行数到 DDR 后,VI 上报一个中断,把图像发给后端模块处理,可以减少延时,但没有和低延时一样的硬件机制保证后端模块读图像不会出错。

6. VPSS

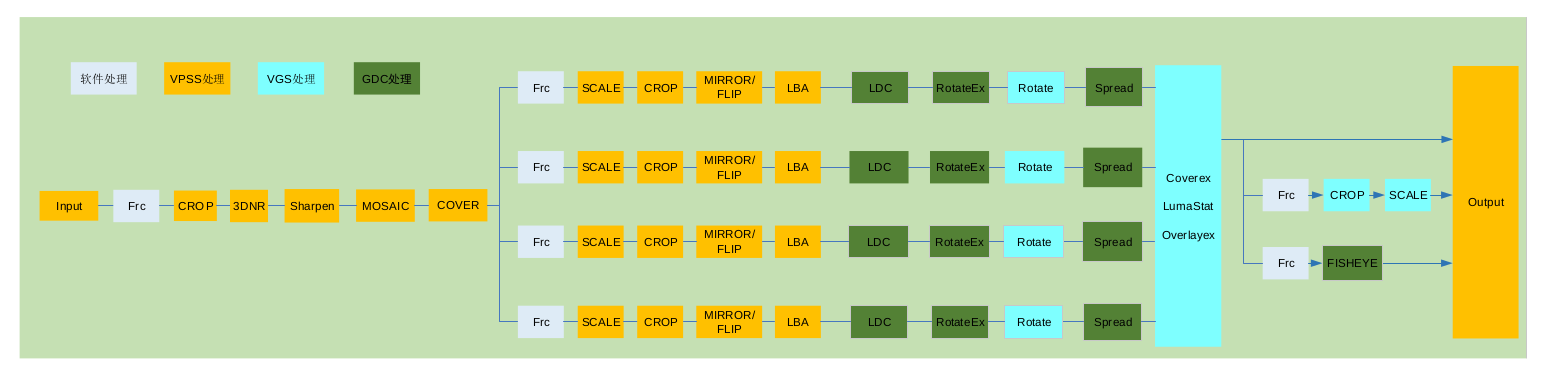

VPSS(Video Process Sub-System)是视频处理子系统,支持的具体图像处理功能包括 FRC(Frame Rate Control)、CROP、Sharpen、3DNR、Scale、像素格式转换、LDC、Spread、固定角度旋转、任意角度旋转、鱼眼校正、Cover/Coverex、Overlayex、Mosaic、Mirror/Flip、HDR、Aspect Ratio、压缩解压等。

vpss 的数据处理流程如下:

vpss 相关基本概念:

- GROUP

VPSS 对用户提供组(GROUP)的概念。最大个数请参见 VPSS_MAX_GRP_NUM 定义,各 GROUP 分时复用 VPSS 硬件,硬件依次处理各个组提交的任务。 - CHANNEL

VPSS 组的通道。通道分为 2 种:物理通道和扩展通道。VPSS 硬件提供多个物理通道,每个通道具有缩放、裁剪等功能。扩展通道具备裁剪、缩放功能,它通过绑定物理通道,将物理通道输出作为自己的输入,把图像裁剪、缩放成用户设置的目标分辨率输出。 - PIPE

VPSS 组的管道,取值只能为 0。 - FRC

帧率控制,分为 2 种:组帧率控制和通道帧率控制。- 组帧率控制:用于控制各 GROUP 对输入图像的接收。

- 通道帧率控制:用于控制各个物理通道和扩展通道图像的处理。

- CROP

裁剪,分为 3 种:组裁剪、物理通道裁剪以及扩展通道裁剪。- 组裁剪,VPSS 对输入图像进行裁剪。

- 物理通道裁剪,VPSS 对各个物理通道的输出图像进行裁剪。

- 扩展通道裁剪,VPSS 调用 VGS 对扩展通道的输出图像进行裁剪

- Scale

缩放,对图像进行缩小放大。物理通道水平、垂直最大支持 15 倍缩小,最大支持 16 倍放大;扩展通道水平、垂直最大支持 30 倍缩小,最大支持 16 倍放大。 - Mirror/Flip

Mirror 即水平镜像,Flip 即上下翻转。可使用 Mirror+Flip 实现 180°旋转。 - Mosaic

马赛克,对 VPSS 的输出图像填充马赛克块。 - Cover

视频遮挡区域,对 VPSS 的输出图像填充纯色块。 - Overlayex

视频叠加区域,调用 VGS 对 VPSS 通道的输出图像叠加位图,支持位图格式 ARGB4444、ARGB1555、ARGB8888、2BPP(仅 Hi3516EV200/Hi3516EV300 支持)。 - 3DNR

去噪。通过参数配置,把图像中的高斯噪声去除,使得图像变得平滑,有助于降低编码码率。Hi3559AV100ES/Hi3559AV100 不支持。 - 固定角度旋转

支持 0 度、90 度、180 度以及 270 度固定角度的旋转功能。 - 任意角度旋转

支持任意角度的旋转功能。Hi3559AV100ES/Hi3559AV100/Hi3516EV200 不支持。 - LDC

对输入图像做镜头畸变校正。Hi3559AV100ES/Hi3559AV100/Hi3516EV200 不支

持。 - Spread

对输入图像做展宽处理。Hi3559AV100ES/Hi3559AV100/Hi3516EV200 不支持。 - 鱼眼校正

仅 Hi3519AV100/Hi3516CV500/Hi3516AV300/Hi3516DV300 支持。 - Aspect Ratio

幅形比,指定输出画面相对于输入画面的宽高纵横比。

6.1 从 VPSS 模块中获取帧数据

我们需要进行 AI 算法运行的时候,需要从 VPSS 模块中获取帧数据,输入给算法模块进行处理。帧数据的获取大概如下:

1 | // 1. 获取帧数据,保存到 pstVideoFrame 中。 |

7. VO

VO(Video Output,视频输出)模块主动从内存相应位置读取视频和图形数据,并通过相应的显示设备(HDMI等)输出视频和图形。

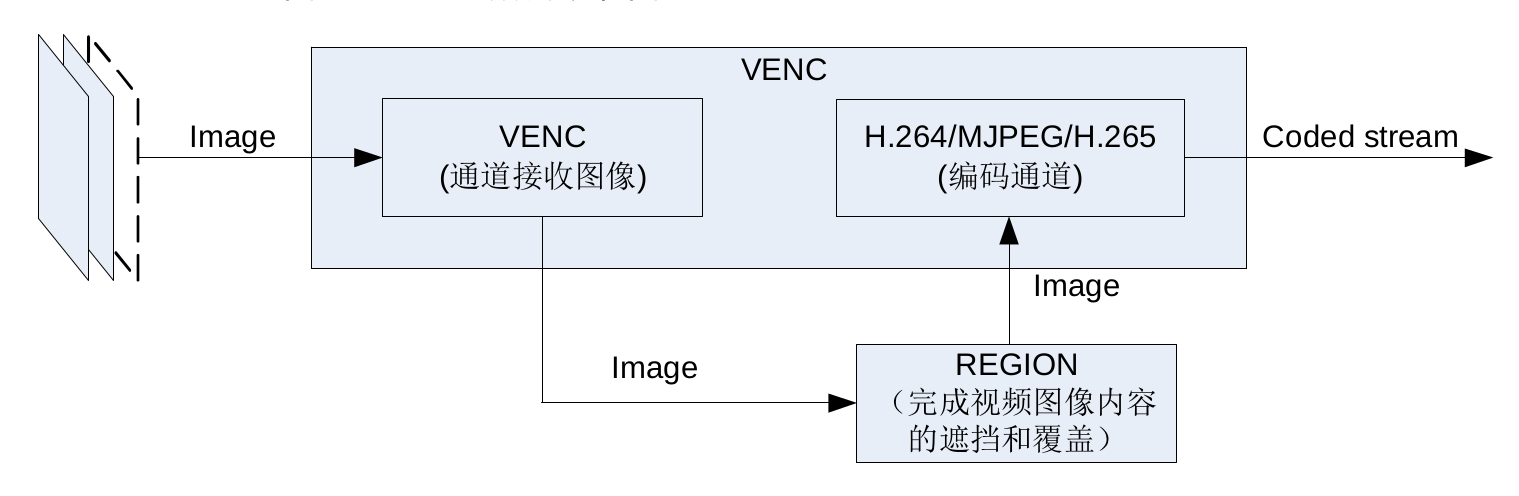

8. VENC

视频编码模块支持多路实时编码,且每路编码独立,编码协议和编码 profile 可以不同。本模块支持视频编码同时,调度 Region 模块对编码图像内容进行叠加和遮挡。

视频编码流程如下:

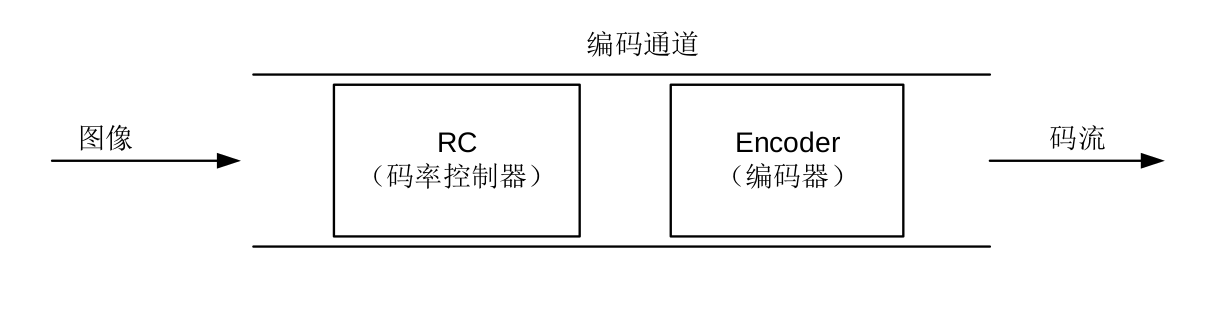

其中编码通道处理流程如下:

venc 相关基本概念:

- 编码通道

编码通道作为基本容器,保存编码通道的多种用户设置和管理编码通道的多种内部资源。编码通道完成图像转化为码流的功能,具体由码率控制器和编码器协同完成。这里的编码器指的是狭义上的编码器,只完成编码功能。码率控制器提供了对编码参数的控制和调整,从而对输出码率进行控制。 - 码率控制

码率控制器实现对编码码率进行控制。从信息学的角度分析,图像的压缩比越低,压缩图像的质量越高;图像压缩比例越高,压缩图像的质量越低。对于场景变化的真实场景,图像质量稳定,编码码率会波动;编码码率稳定,图像质量会波动。以 H.264 编码为例,通常图像 Qp 越低,图像的质量越好,码率越高;图像 Qp 越高,图像质量越差,码率越低。

码率控制是针对连续的编码码流而言,所以,JPEG 协议编码通道不包括码率控制功能。

码率控制器分别提供了对 MJPEG 协议编码通道 CBR、VBR、FIXQP 三种码率控制模式,H.264/H.265 协议编码通道 CBR、VBR、AVBR、QVBR、CVBR、FIXQP、QPMAP 七种码率控制模式,对图像质量和码率进行调节,对于 H.264/H.265/协议通道的 QPMAP 模式,码控的策略由用户决定。

8.1 从 VENC 模块中获取帧数据

VENC 编码完成后,需要 uvc, rtsp 等模块从 VENC 中获取帧数据,然后对外发送。帧数据的获取流程大概如下:

1 | // 1. 查询 VENC 编码状态, VENC_CHN_STATUS_S.u32CurPacks 为当前帧的 package 数量。为 0 时说明还没编码好,等会再查询。 |

9. VI, VPSS 工作模式

VI 和 VPSS 各自的工作模式分为在线,离线,并行模式,工作模式说明如下:

| 模式 | VI_CAP 与 VI_PROC | VI_PROC 与 VPSS |

|---|---|---|

| 在线模式 | VI_CAP 与 VI_PROC 之间在线数据流传输,此模式下 VI_CAP不会写出 RAW 数据到 DDR,而是直接把数据流送给VI_PROC。 | VI_PROC 与 VPSS 之间的在线数据流传输,在此模式下 VI_PROC不会写出 YUV 数据到 DDR,而是直接把数据流送给 VPSS。 |

| 离线模式 | VI_CAP 写出 RAW 数据到DDR,然后 VI_PROC 从 DDR 读取 RAW 数据进行后处理。 | VI_PROC 写出 YUV 数据到DDR,然后 VPSS 从 DDR 读取 YUV 数据进行后处理。 |

从以上的描述来看在线模式和离线模式的主要差别是是否将数据写出 DDR。在线模式时 VI 进行时序解析后直接在芯片内部将数据传递到VPSS,中间无DDR 写出的过程。在线模式可以省一定的带宽和内存,降低端到端的延时。但是,在线模式时,因为VI 不写出数据到DDR,无法进行CoverEx、OverlayEx、Rotate、LDC 等操作,需要在VPSS 各通道写出后再进行Rotate/LDC 等处理,而且有些功能只在离线下能支持,比如DIS。所以使用在线模式还是离线模式需要根据具体需求来决定。如果追求低延时,那自然要使用在线模式。